Siemens PADS Standard Plus VX.2.15 Win x64

Free Download Siemens PADS Standard Plus VX.2.15 | 6.8 Gb

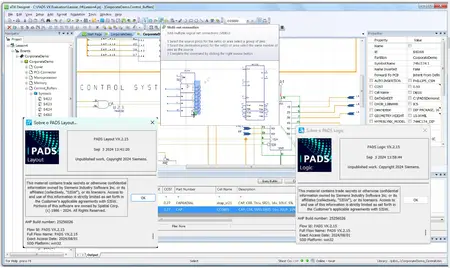

Mentor Graphics Corporation, a Siemens business, is pleased to announce the availability ofPADS VX.2.15. This is primarily a release aimed at adding new functionality and fixing customers' logged defects - Service Requests (SRs)

Owner:Mentor Graphics Corporation, a Siemens business

Product Name:PADS

Version:VX.2.15 Standard Plus

Supported Architectures:x64

Website Home Page :

https://eda.sw.siemens.com/Languages Supported:english

System Requirements:Windows *

Size:6.8 Gb.

New Features Introduced in PADS VX.2.15

The following new products, features, and enhancements are introduced in the PADS VX.2.15 release.

HyperLynx AMS

HyperLynx AMS (formerly PADS AMS) includes the following updates in release PADS VX.2.15.

PADS AMS rebranded as HyperLynx AMS

The PADS AMS simulator is rebranded as HyperLynx AMS. This is a name change only to better align the simulator with the analysis and verification tool family within the Electronic Board Systems division in Siemens EDA. You will now see "HyperLynx AMS" rather than "PADS AMS" in menus and dialogs when installing and using the tool.

Reorganized parameter list in the Select Parameter dialog

When setting up sweep-based analyses, the Select Parameter dialog helps you choose parameters to change during the simulation. Net names in the Select Parameter dialog are now organized hierarchically by component name.

Removed assigned pins from the pin mapping tool list

When you select a simulation model for a symbol, you need to ensure the symbol pins are correctly connected to the model ports. The pin mapping tool in the Model and Symbol Wizard and Edit Model Properties dialogs helps with this mapping. In release VX.2.15, the pin mapping tool is updated so once a symbol pin is selected for mapping, it no longer appears in the list of possible pins to assign.

HyperLynx DRC

The sections below provide details of changes in this version of the HyperLynx DRC products.

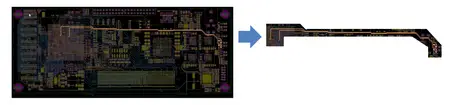

Export CCE file with Area crop function for HL SI

New CCE export support improves rule performance by truncating designs

- Object-based Area cropping - Cutting out design at a fixed distance from specific objects of interest (e.g., nets, pins, etc.)

- Coordinate-base Area cropping - Cutting out the design by specifying coordinates

Improved accuracy

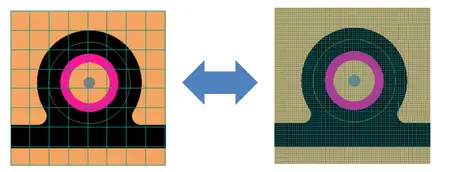

One Nanometer Resolution

- Improve geometric resolution from 10nm to 1nm

- Increase accuracy during analysis operations

- Aligns resolution expectation with Xpedition and other EDA flows

- New Trace Modeler - improves calculation to more closely match the SI product

- Improved accuracy of the Assembly Component Outlines within the Allegro Translation

HyperLynx SI/PI/Thermal

This release contains the following improvements along with numerous defect fixes and Security improvements.

General Improvements

- Simplified configuration of IBIS-AMI models for DDR5/LPDDR5(X) simulation

- IBIS-AMI simulation of command/address bus DDR5/LPDDR5(X) simulation

- Easier setup for DDR5/LPDDR5(X) simulation when using IBIS-only models

DDRx

- The DDRx batch wizard GUI has been enhanced to simplify the user experience. Prior to VX.2.15, the configuration of IBIS-AMI models was spread across multiple pages and required careful selection of controller/DRAM. Now in VX.2.15, the configuration of IBIS-AMI models for an operation can be viewed and configured on a single page of the wizard. The DDRx batch wizard will now support IBIS-AMI simulation of the unbuffered command/address bus for DDR5/LPDDR5(X). Prior to VX.2.15, this capability was available only for registered DIMM (RDIMM). Now in VX.2.15, HyperLynx can incorporate effects such as controller Tx equalization and IBIS-AMI jitter/noise parameters into the simulation of the command/address bus.

DDR5

- For DDR5/LPDDR5(X) simulations, the DDRx batch wizard will now automatically substitute pass-through AMI executables when an IBIS-only buffer model is detected. Prior to VX.2.15, this required manual editing of the IBIS model text file. By making the automatic substitution, the user saves time and frustration and can focus on progressing to simulation results.

Modern 3D Board Viewing Capability

- Standard integrated part of SI/PI

- Full 3D Board View or Partial region view

- Select and highlight nets in sync between 2D and 3D views

- Improved emphasizing and transparency controls for objects of interest

SERDES Compliance

- New Compliance Wizard protocol support for:

. OIF CEI-224G-MR-PAM4

. PCIe Gen 6 Add-in-Card

. System Board channels

- Supports Rx FFE algorithms of COM 4.1

- HTML report adds Rx FFE worst/best case tap weight table

- Improved 100G Ethernet and OIF COM algorithms

- Updated protocols including fixes

. 100G Ethernet and OIF

. PCIe Gen 4,5 and 6

. MIPI D-PHY Modes 0-4

. 10GBASE-KR and 40GBASE-KR4

PADS (Personal Automated Design Solutions)provide an easy-to-use environment that helps solve the PCB design challenges you meet every day. Using PADS, you will get your job done faster and better, while saving costs.

PADS Standard Plusincludes advanced circuit simulation with comprehensive analysis for analog, mixed-signal, and mixed-technology PCB circuits. PADS Standard Plus is ideal for less complex board design, and where cost savings is a high priority. Easy-to-use schematic and layout translators help import libraries and designs from your current toolset, whether it's Allegro, Altium Designer, CADSTAR, OrCAD, P-CAD, or Protel.

PADS Professional PCB Design Software

Siemens Digital Industries Softwareis a leading global provider of product life cycle management (PLM) software and services with 7 million licensed seats and 71,000 customers worldwide. Headquartered in Plano, Texas, Siemens Digital Industries Software works collaboratively with companies to deliver open solutions that help them turn more ideas into successful products.

Links are Interchangeable - No Password - Single Extraction